Xilinx, Inc. announced a new product category that it calls “adaptive compute acceleration platform” (ACAP) that is is claimed to go ‘far beyond’ the capabilities of an FPGA, it’s traditional product category.

The firm describes an ACAP as a highly integrated multi-core heterogeneous compute platform that can be changed at the hardware level to adapt to the needs of a wide range of applications and workloads. The company claims that an ACAP’s adaptability, which can be exploited dynamically during operation, delivers levels of performance and performance per-watt that is unmatched by CPUs or GPUs.

Well-suited applications include video transcoding, database, data compression, search, AI inference, genomics, machine vision, computational storage and network acceleration. Software and hardware developers will be able to design ACAP-based products for end point, edge and cloud applications. The first ACAP product family, codenamed “Everest,” will be developed in TSMC 7nm process technology and will tape out later this year, the company said, with customer shipments in 2019.

ACAP Technical Details

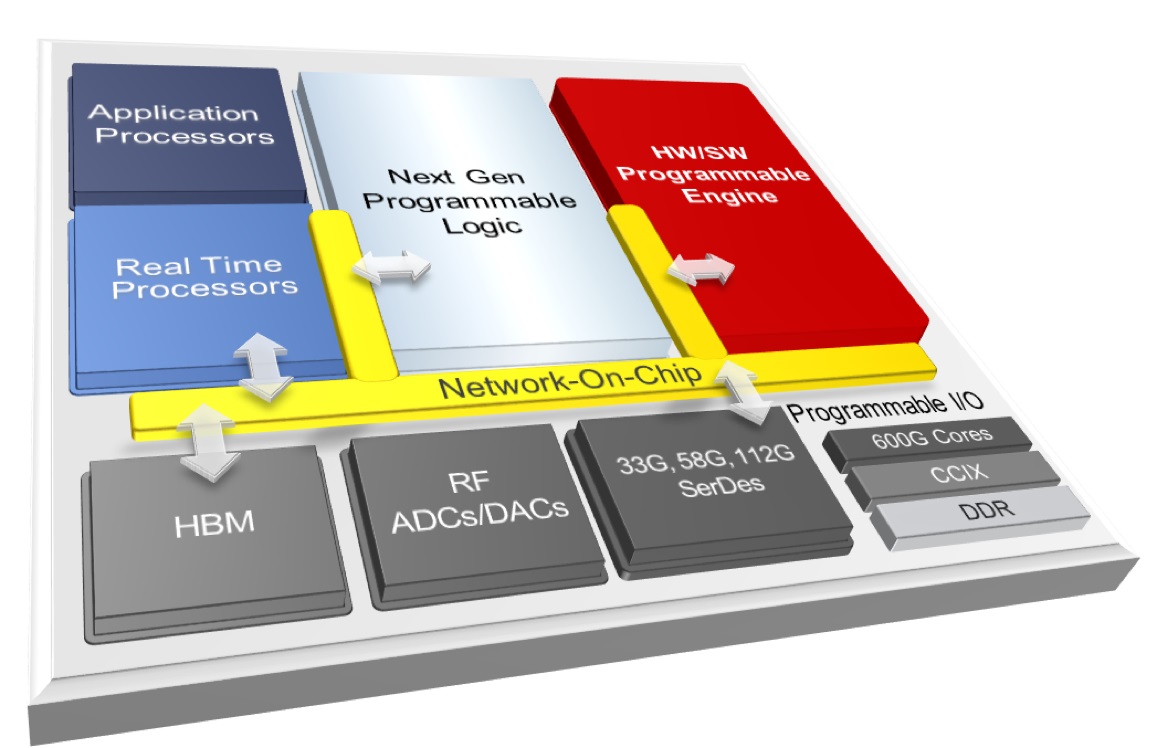

An ACAP has – at its core – a new generation of FPGA fabric with distributed memory and hardware-programmable DSP blocks, a multicore SoC, and one or more software programmable, yet hardware adaptable, compute engines, all connected through a network on chip (NoC). An ACAP also has highly integrated programmable I/O functionality, ranging from integrated hardware programmable memory controllers, advanced SerDes technology and leading edge RF-ADC/DACs, to integrated High Bandwidth Memory (HBM) depending on the device variant.

Software developers will be able to target ACAP-based systems using tools like C/C++, OpenCL and Python. An ACAP can also be programmable at the RTL level using FPGA tools.

Patrick Moorhead, founder, Moor Insights & Strategy said

“This is what the future of computing looks like. We are talking about the ability to do genomic sequencing in a matter of a couple of minutes, versus a couple of days. We are talking about data centers being able to program their servers to change workloads depending upon compute demands, like video transcoding during the day and then image recognition at night. This is significant.”

ACAP has been under development for four years at an accumulated R&D investment of over one billion dollars, Xilinx said. There are currently more than 1,500 hardware and software engineers at Xilinx designing “ACAP and Everest.” Software tools have been delivered to key customers. “Everest” will tape out in 2018 with customer shipments in 2019.

“Everest” Performance Improvements

“Everest” is expected to achieve 20x performance improvement on deep neural networks compared to today’s latest 16nm Virtex VU9P FPGA. “Everest”-based 5G remote radio heads will have 4x the bandwidth versus the latest 16nm-based radios.

Analyst Comment

This looks like an interesting development for video – the company’s detailed performance notes claim a 10X improvement in HEVC transcoding. This concept is an extension of the previous integration of dedicated processing with fully programmable circuitry that we have seen from Xilinx in recent years. (Xilinx Has Advantages for UltraHD and 8K) (BR)