The Video Electronics Standards Association (VESA®) today published the Embedded DisplayPort (eDP) Standard version 1.4a. Replacing eDP v1.4, published in February 2013, eDP 1.4a enables a higher video data transfer rate for increased panel resolution, greater color depth and higher refresh rates.

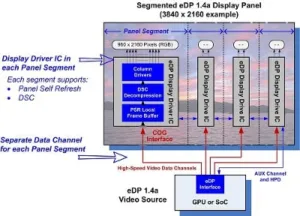

It also incorporates the VESA Display Stream Compression (DSC) Standard v1.1, and includes a new segmented panel architecture that enables higher panel integration. These and other refinements were made to the eDP 1.4a standard to take advantage of higher GPU video performance and newer display technologies, while also enabling reduced system power and form factor.

The eDP v1.4a standard leverages the VESA DisplayPort (DP) Standard v1.3, published in September 2014, as a base specification. That standard’s new higher HBR3 link rate, which operates at 8.1 Gbps per lane, is now also part of eDP v1.4a. With both HBR3 and the DSC v1.1 standard included, the latest eDP standard can support embedded panels with up to 8K resolution. For embedded display applications, DSC is most often used to decrease video interface data rate or wire count, as well as reduce display frame buffer size, thereby reducing system power usage to extend battery life. It also enables reductions in system complexity and form factor.

The new Embedded DisplayPort (eDP) v1.4a specification from VESA supports Segmented Panel display architectures, which are designed to enable thinner, lighter and lower-cost panels that use less power.

An entirely new feature in eDP v1.4a is “Multi-SST Operation,” or MSO, which supports a new type of display architecture that VESA calls “Segmented Panel Display.” Segmented Panel Display is designed to enable thinner, lighter and lower-cost panels that use less power. In operation, MSO allows the four high-speed eDP data lanes within the eDP interface to be divided up between either two or four independent panel segments. For lower resolutions, two lanes can be used to support two panel segments. This panel segmentation enables a higher level of integration on high-resolution displays; each segment can contain a separate timing controller with integrated source drivers.

According to Vice President Bong-Hyun You of Samsung Display Co., Ltd., “The Multi-SST Architecture enables greater design flexibility and power savings in new LCD panel technologies for embedded high resolution displays. Samsung proposed this feature in order to permit panel makers to make even broader usage of the eDP interface in advanced panels, as well as reduce panel thickness, reduce power draw, and reduce cost.”

eDP 1.4a also includes refinements to the partial update capability for Panel Self Refresh (PSR) that was introduced in eDP 1.4. Partial update enables the system video processor, or GPU, to update only the portion of the display that has changed since the video frame update, further saving system power.

According to Craig Wiley, senior director of marketing at Parade Technologies, VESA board member, and editor for eDP 1.4a, “The adoption of eDP for embedded displays is now positioned for growth as eDP 1.4a has become highly optimized, especially at resolutions above quad HD. Compared to other embedded interfaces, it has the richest feature set along with the lowest power, wire count and EMI radiation, particularly when used with high-resolution panels. It will continue to evolve, along with DisplayPort, but with its own unique features specifically optimized for embedded applications such as all-in-one PCs, notebooks, tablets and smart phones.”

It is anticipated that eDP 1.4a will be used within systems by 2016. The eDP v1.4a Standard is available to VESA members. For more information, please visit www.vesa.org.